We use Dijkstra’s algorithm for buffered routing because it tends to be very fast and efficient, especially for early planning and estimation. I think you’ll appreciate the speed of this approach, as it can quickly find paths in a buffer graph where edges represent buffer-to-buffer paths. This makes it particularly useful when we need to quickly estimate routing paths without getting bogged down by too many details.

Limitation of Dijkstra’s algorithm

However, one limitation is that Dijkstra-based techniques can’t easily account for all the details that dynamic programming algorithms can, such as varying wire sizing resources from channel to channel. You might find that these details are important in more precise or complex routing scenarios. Despite this, the flexibility in estimating buffer input-to-input delays is a significant advantage.

Delay Reduction to Cost Ratio (DRCR)

There are two key problems addressed using Dijkstra’s algorithm in this context: finding a minimum-delay path and finding a tradeoff between delay and cost. The first approach focuses on pre-computing minimum-delay wire sizing configurations, while the second deals with the Delay Reduction to Cost Ratio (DRCR) problem. By varying parameters like Dref, we can explore different solutions on the Lower Convex Hull of non-dominated paths, allowing for efficient optimization based on our specific objectives.

Difference between Dijkstra’s Algorithms and Bellman-Ford Algorithm

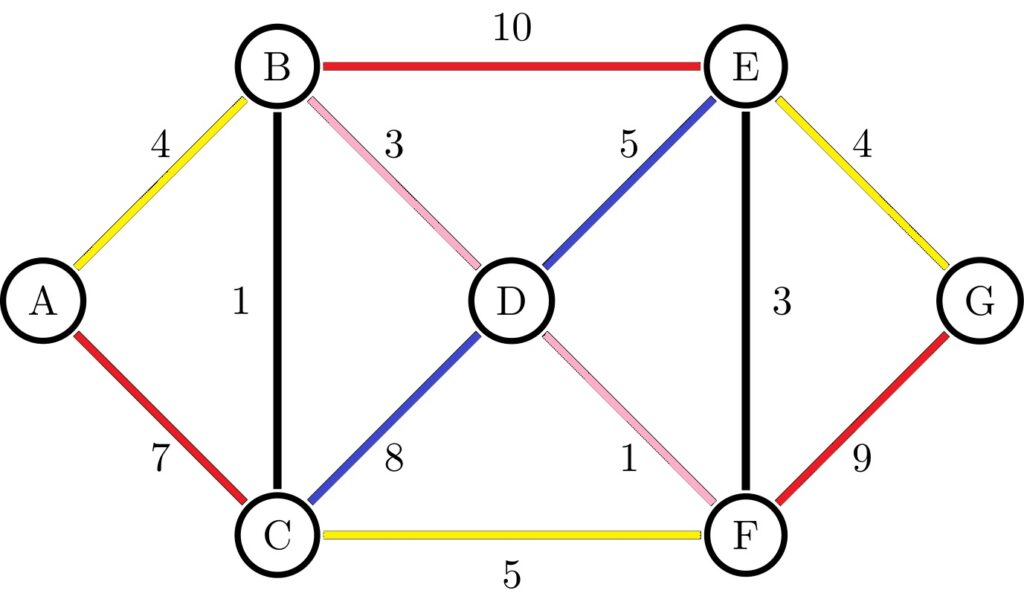

If you’re dealing with graphs that have non-negative edge weights, Dijkstra’s algorithm is the one we usually choose—it’s optimized for those conditions. On the other hand, Bellman-Ford is a better option when your graph includes negative edge weights, and it can even detect negative-weight cycles.

Dijkstra’s uses a greedy approach. You and I would select the node with the smallest known distance and then update its neighbors accordingly. Bellman-Ford takes a broader approach—it relaxes all edges in each iteration, checking for shorter paths across the entire graph.

If speed is your concern, Dijkstra’s is faster in most cases. It has a time complexity of O(V²) for dense graphs and O(E log V) when using a priority queue in sparse graphs. In contrast, Bellman-Ford is a bit slower, with a time complexity of O(VE).

This is where you need to be careful. If your graph contains negative edge weights, Dijkstra’s won’t work correctly. But Bellman-Ford can handle those scenarios and even alerts you to negative-weight cycles, which can be critical in some applications.

Difference between Dijkstra’s Algorithms and Floyd-Warshall Algorithm

Dijkstra’s is optimized for finding the shortest path from a single source node to all other nodes in a graph with non-negative edge weights. Floyd-Warshall is designed to find the shortest paths between all pairs of nodes, regardless of the starting point

Dijkstra’s uses a greedy approach, picking the node with the smallest distance and updating its neighbors one at a time. Floyd-Warshall relies on dynamic programming to consider all possible paths between node pairs.

Dijkstra’s has a time complexity of O(V²) for dense graphs and O(E log V) for sparse graphs (with a priority queue). Floyd-Warshall has a time complexity of O(V³) because it checks every node pair.

Dijkstra’s does not support negative edge weights and can give incorrect results if they are present. Floyd-Warshall supports negative edge weights, but it cannot process negative-weight cycles.