List of VLSI Project for EC, ECE & ME students

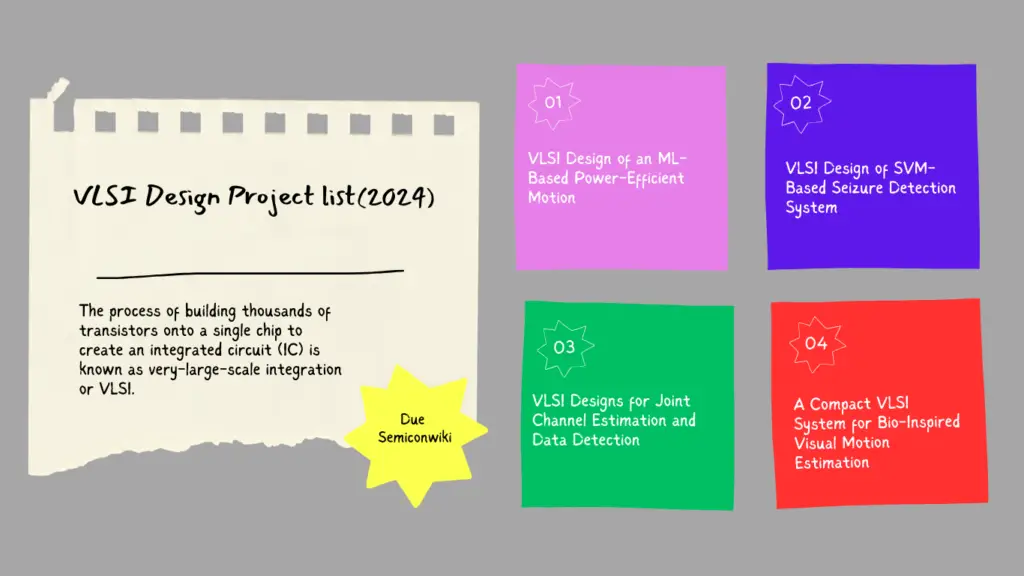

VLSI Projects idea: The process of building thousands of transistors onto a single chip to create an integrated circuit (IC) is known as very-large-scale integration or VLSI. We provide VLSI projects that can be used in real-time solutions through processor optimization, improving system efficiency across the board.

For students and professionals looking to expand their knowledge and skills, working on VLSI projects is an excellent way to explore the complexities of semiconductor design. Below is a list of simple yet impactful VLSI project ideas that can serve as a starting point for your explorations in this fascinating field.

1. Spiking Neural Classifier with Lumped Dendritic Nonlinearity and Binary Synapses: A Current Mode VLSI Implementation and Analysis

- Description: Develop a VLSI implementation of a spiking neural network classifier. Focus on incorporating lumped dendritic nonlinearity and binary synapses to analyze performance in current mode.

2. Accurate Performance Evaluation of VLSI Designs with Selected CMOS Process Parameters

- Description: Conduct a performance evaluation of VLSI designs using specific CMOS process parameters. Analyze and compare the results to optimize design efficiency.

3. A VLSI On-Chip Analog High-Order Low-Pass Filter Performance Evaluation Strategy

- Description: Design and evaluate an on-chip analog high-order low-pass filter. Focus on performance metrics such as cutoff frequency, attenuation, and power consumption.

4. A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures

- Description: Explore the design and integration challenges of silicon photodiodes for high-speed communication. Investigate low-dimensional structures and their impact on VLSI integration.

5. VLSI Design of an ML-Based Power-Efficient Motion Estimation Controller for Intelligent Mobile Systems

- Description: Implement a machine learning-based motion estimation controller for mobile systems. Emphasize power efficiency and real-time processing capabilities.

6. VLSI Design of SVM-Based Seizure Detection System with On-Chip Learning Capability

- Description: Develop a VLSI system for seizure detection using Support Vector Machine (SVM) algorithms. Incorporate on-chip learning to improve detection accuracy and adaptability.

7. VLSI Designs for Joint Channel Estimation and Data Detection in Large SIMO Wireless Systems

- Description: Design a VLSI system for joint channel estimation and data detection in large Single Input Multiple Output (SIMO) wireless systems. Focus on improving signal quality and data throughput.

8. VLSI Design and Implementation of Reconfigurable 46-Mode Combined-Radix-Based FFT Hardware Architecture for 3GPP-LTE Applications

- Description: Create a reconfigurable hardware architecture for Fast Fourier Transform (FFT) operations in 3GPP-LTE applications. Implement combined-radix methods to enhance performance.

9. A Compact VLSI System for Bio-Inspired Visual Motion Estimation

- Description: Develop a compact VLSI system inspired by biological visual processing mechanisms for motion estimation. Focus on real-time applications and power efficiency.

10. A Variable-Clock-Cycle-Path VLSI Design of Binary Arithmetic Decoder for H.265/HEVC

- Description: Design a VLSI binary arithmetic decoder with variable clock cycle paths for H.265/HEVC video compression standards. Aim for high speed and low power consumption.

Related page: VLSI Design Questions with Answers (2024)

11. VLSI Architecture Exploration of Guided Image Filtering for 1080P@60Hz Video Processing

- Description: Investigate the VLSI architecture for guided image filtering used in high-definition video processing. Optimize for performance at 1080P resolution and 60Hz refresh rates.

12. A Neuromorphic VLSI Circuit for Spike-Based Random Sampling

- Description: Create a neuromorphic VLSI circuit capable of spike-based random sampling. Explore applications in brain-inspired computing and data analysis.

13. Thermal Management of Batteries Using Supercapacitor Hybrid Architecture with Idle Period Insertion Strategy

- Description: Design a thermal management system for batteries utilizing a supercapacitor hybrid architecture. Implement an idle period insertion strategy to enhance battery longevity.

14. Data Reuse Buffer Synthesis Using the Polyhedral Model

- Description: Synthesize a data reuse buffer using the polyhedral model. Focus on optimizing data access patterns to improve memory bandwidth and reduce latency.

15. High-Performance Architecture Using Fast Dynamic Reconfigurable Accelerators

- Description: Develop a high-performance architecture employing fast dynamic reconfigurable accelerators. Aim for applications in computationally intensive tasks.

16. Dynamic Reconfiguration of Thermoelectric Generators for Vehicle Radiators Energy Harvesting Under Location-Dependent Temperature

- Description: Implement dynamic reconfiguration techniques for thermoelectric generators used in vehicle radiator energy harvesting. Address challenges posed by location-dependent temperature variations.

17. Optimizing the Convolution Operation to Accelerate Deep Neural Networks on FPGA

- Description: Optimize convolution operations for deep neural networks implemented on FPGAs. Focus on achieving high throughput and low latency.

18. On the Analysis and the Mitigation of Power Supply Noise and Power Distribution Network Impedance Variation for Scan-Based Delay Testing Techniques

- Description: Analyze and mitigate power supply noise and impedance variations in power distribution networks for scan-based delay testing techniques. Aim for improved reliability and accuracy.

19. Low Overhead Warning Flip-Flop Based on Charge Sharing for Timing Slack Monitoring

- Description: Design a low overhead warning flip-flop leveraging charge sharing for monitoring timing slack in VLSI circuits. Focus on low power consumption and high precision.

20. A Changing-Reference Parasitic-Matching Sensing Circuit for 3-D Vertical RRAM

- Description: Develop a changing-reference parasitic-matching sensing circuit for 3-D vertical resistive random-access memory (RRAM). Emphasize accuracy and reliability.

21. Toward Energy-Efficient Stochastic Circuits Using Parallel Sobol Sequences

- Description: Create energy-efficient stochastic circuits using parallel Sobol sequences. Explore applications in probabilistic computing and random number generation.

22. Design and Analysis of Energy-Efficient and Reliable 3-D ReRAM Cross-Point Array System

- Description: Design and analyze a 3-D ReRAM cross-point array system focusing on energy efficiency and reliability. Address challenges in scaling and integration.

23. Secure Double Rate Registers as an RTL Countermeasure Against Power Analysis Attacks

- Description: Implement secure double rate registers as an RTL countermeasure against power analysis attacks. Enhance the security and robustness of VLSI designs.

24. A Flexible and Energy-Efficient Convolutional Neural Network Acceleration with Dedicated ISA and Accelerator

- Description: Develop a flexible and energy-efficient accelerator for convolutional neural networks with a dedicated instruction set architecture (ISA). Optimize for various machine learning tasks.

25. Low-Complexity VLSI Design of Large Integer Multipliers for Fully Homomorphic Encryption

- Description: Design a low-complexity VLSI system for large integer multipliers used in fully homomorphic encryption. Focus on achieving high performance with minimal hardware resources.

26. Reducing Rollback Cost in VLSI Circuits to Improve Fault Tolerance

- Description: Develop techniques to reduce rollback costs in VLSI circuits, thereby improving fault tolerance and system reliability.

27. A 900 MHz, 3.5mW 8 bit Pipelined Sub-ranging ADC Combining Flash ADC and TDC

- Description: Design an 8-bit pipelined sub-ranging analog-to-digital converter (ADC) combining flash ADC and time-to-digital converter (TDC) techniques. Target low power consumption and high-speed operation.

28. A High-Speed 2 Bit/Cycle SAR ADC with Time Domain Quantization

- Description: Create a high-speed successive approximation register (SAR) ADC capable of processing 2 bits per cycle with time domain quantization. Focus on speed and accuracy.

29. A Linearity-Improved 8-bit 320-MS/s SAR ADC with Metastability Immunity Technique

- Description: Design a linearity-improved 8-bit SAR ADC with a sampling rate of 320 MS/s, incorporating metastability immunity techniques to enhance performance.

30. A Low Power Forward and Reverse Body Bias Generator in CMOS 40nm

- Description: Develop a low power forward and reverse body bias generator in 40nm CMOS technology. Aim for efficient body biasing to improve transistor performance.