Memory Address Bus width question

Yes, each memory generation typically has a different address bus width, which depends on the word count of the DRAM IC. The width of the address bus determines the number of memory locations that can be addressed. This factor does limit the supported memory size of each generation to some extent. However, techniques like serializing the address across multiple clock cycles, as seen in DDR5 and GDDR7, can mitigate this limitation.

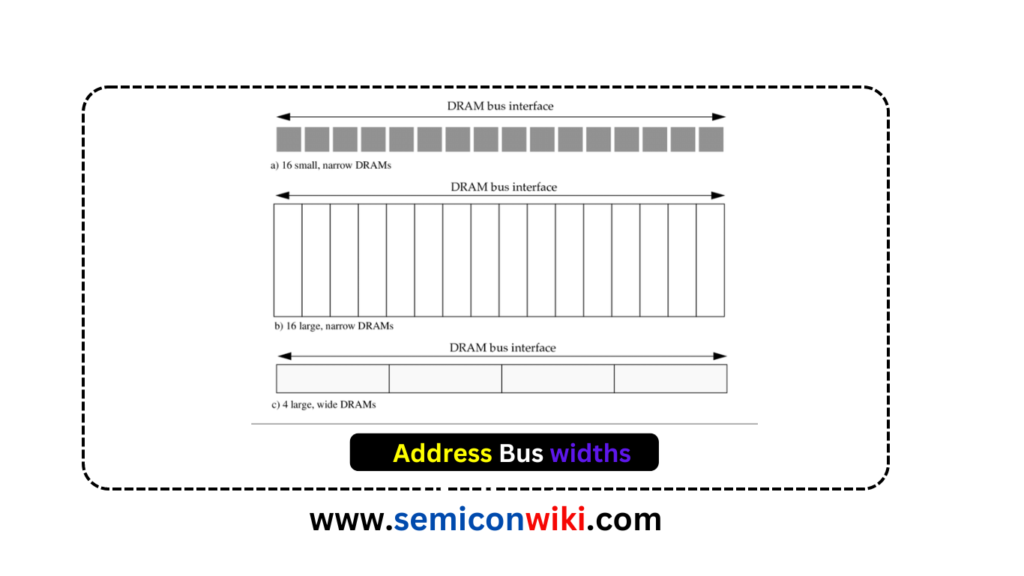

Address Bus widths (Image source)

The memory controller interacts with the memory sticks through an MMU (Memory Management Unit). which translates the DRAM segment of the physical address space into controller and rank, bank, row addresses.

Read also: What is an Integrated Circuit (IC)?

The memory controller then takes requests from the processors and I/O system, generates DRAM-specific commands, schedules them, and issues them to the DRAM.