Memory Address Bus width question with Answer

When we look at how much memory a CPU can access directly, it all comes down to the width of the memory address bus. If you or I are working with a wider address bus, that simply means the CPU can reach more memory locations. In fact, if the bus is n bits wide, then we can access up to 2ⁿ different memory addresses. So, the wider the bus, the more memory we can use.

When I first started learning about memory technology, I was amazed at how crucial the address bus width is to modern computing. If you’ve ever wondered how your computer or gaming console manages memory, this is a great place to start. The address bus width determines how many memory locations a system can access, and it plays a huge role in defining the memory capabilities of each DRAM generation, like DDR4, DDR5, and GDDR7.

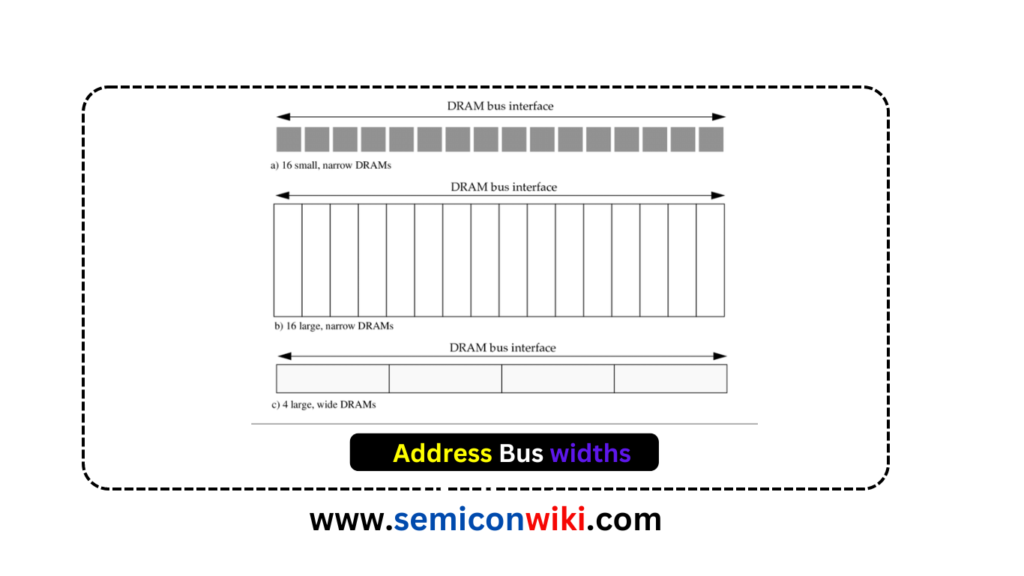

Address Bus widths (Image source)

What Is Address Bus Width and Why Does It Matter?

The address bus width is the number of bits used to identify memory locations. In simple terms, it’s like a postal system for your computer’s memory, ensuring that data gets delivered to the right “address.” For example:

- A 16-bit address bus can access 65,536 locations.

- A 32-bit address bus can access over 4 billion locations.

When you think about the vast amount of data we handle every day, from gaming to AI applications, it’s clear why this is so important. I often find myself impressed by how modern systems manage these enormous numbers so efficiently.

Read also: What is an Integrated Circuit (IC)?

How Do Modern Systems Overcome Address Bus Limitations?

You might be wondering: If the address bus width limits memory access, how do systems keep up with demand? That’s where techniques like address serialization come in.

In memory generations like DDR5 and GDDR7, instead of widening the address bus indefinitely, engineers use clever methods to serialize the address across multiple clock cycles. This means we can handle more memory without needing a much larger bus. Personally, I find it fascinating how these innovations ensure systems remain powerful and efficient despite physical constraints.

Whether you’re gaming, editing videos, or just scrolling through your phone, the address bus width plays a hidden but vital role in your experience. For those of us who are into tech, understanding this helps us appreciate how our devices manage vast amounts of data so efficiently.

As we explore the next generation of memory technologies, like DDR5 and GDDR7, it’s exciting to see how engineers keep innovating. I’m personally amazed by how far we’ve come, and I bet you are too. The combination of smarter techniques and advanced designs ensures that we’ll continue to see faster and more efficient devices in the future.